Gaa Fet

The present disclosure generally relates to various geometries for gate-all-around transistor devices built on a silicon substrate and, in particular, to transistors that are suitable for low-power applications.

- 全周ゲート fet ( gaa fet )は、チャンネル部分の全側面をゲート材で囲む点を除けば、 finfet と同じようなコンセプトである。 gaa fet は、設計によって、2つ、または3つの有効なゲートを持つことになる。.

- 6.25mm × 6.25mm × 1.82mmL GAa nd 2.42mmB GAp ack - ages. Included in the package are the switching controller, power FET s, inductor and support components. Operating over an input voltage range of 3.6V to 20V, the LTM4622A supports an output voltage range of 1.5V to 12V, set by a single external resistor. Its high efficiency design delivers.

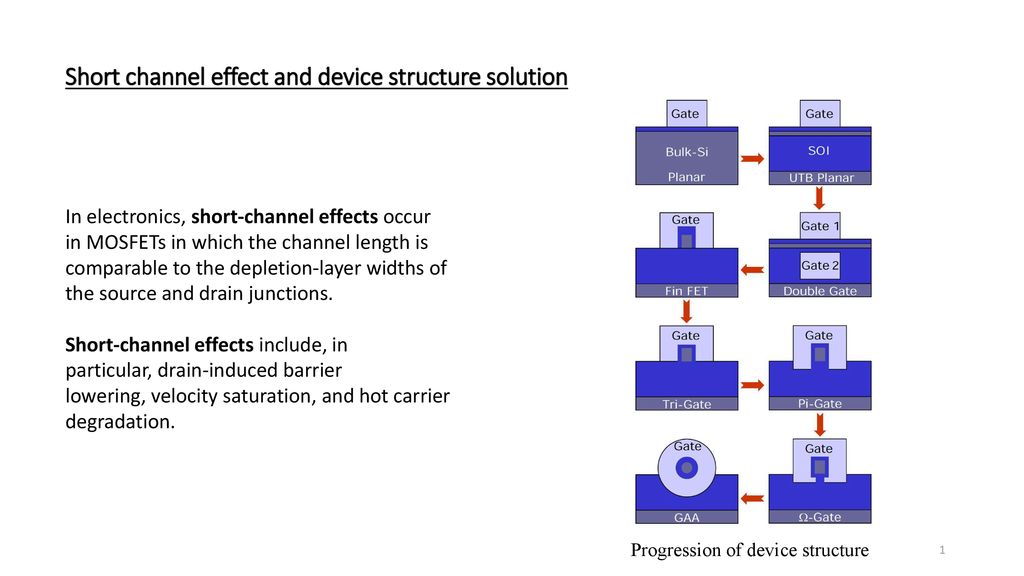

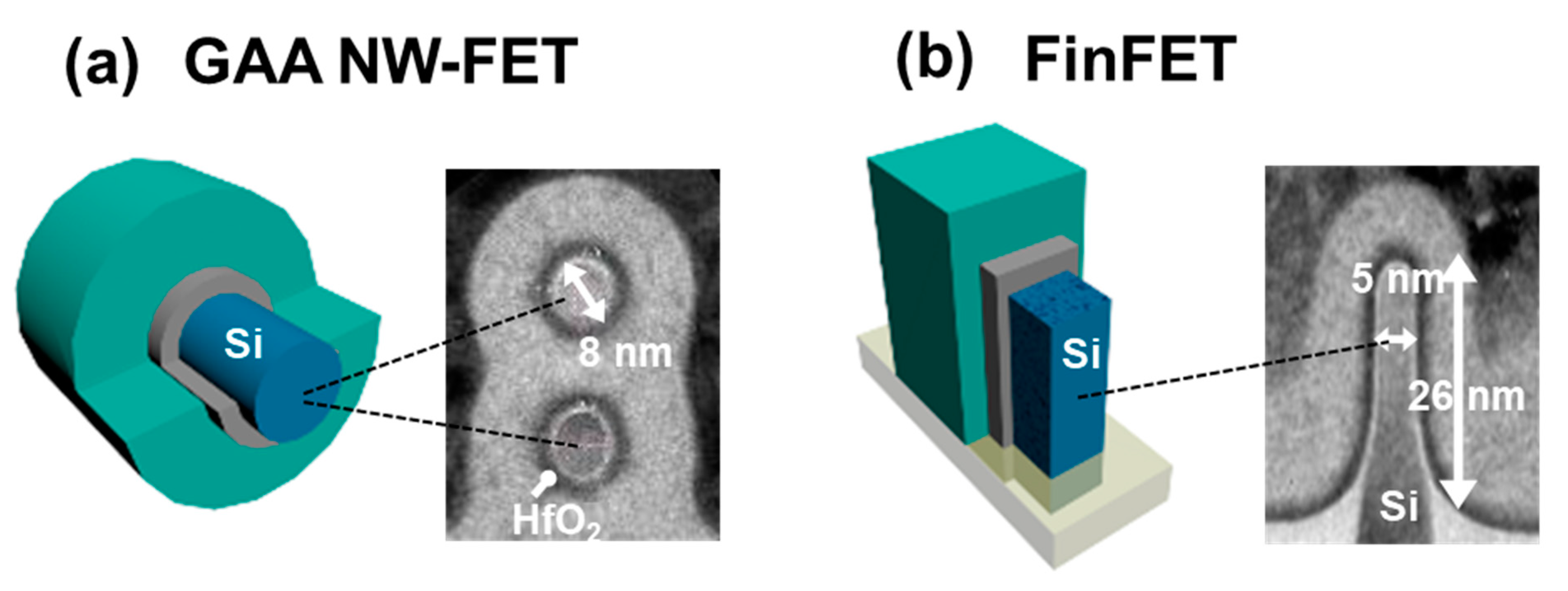

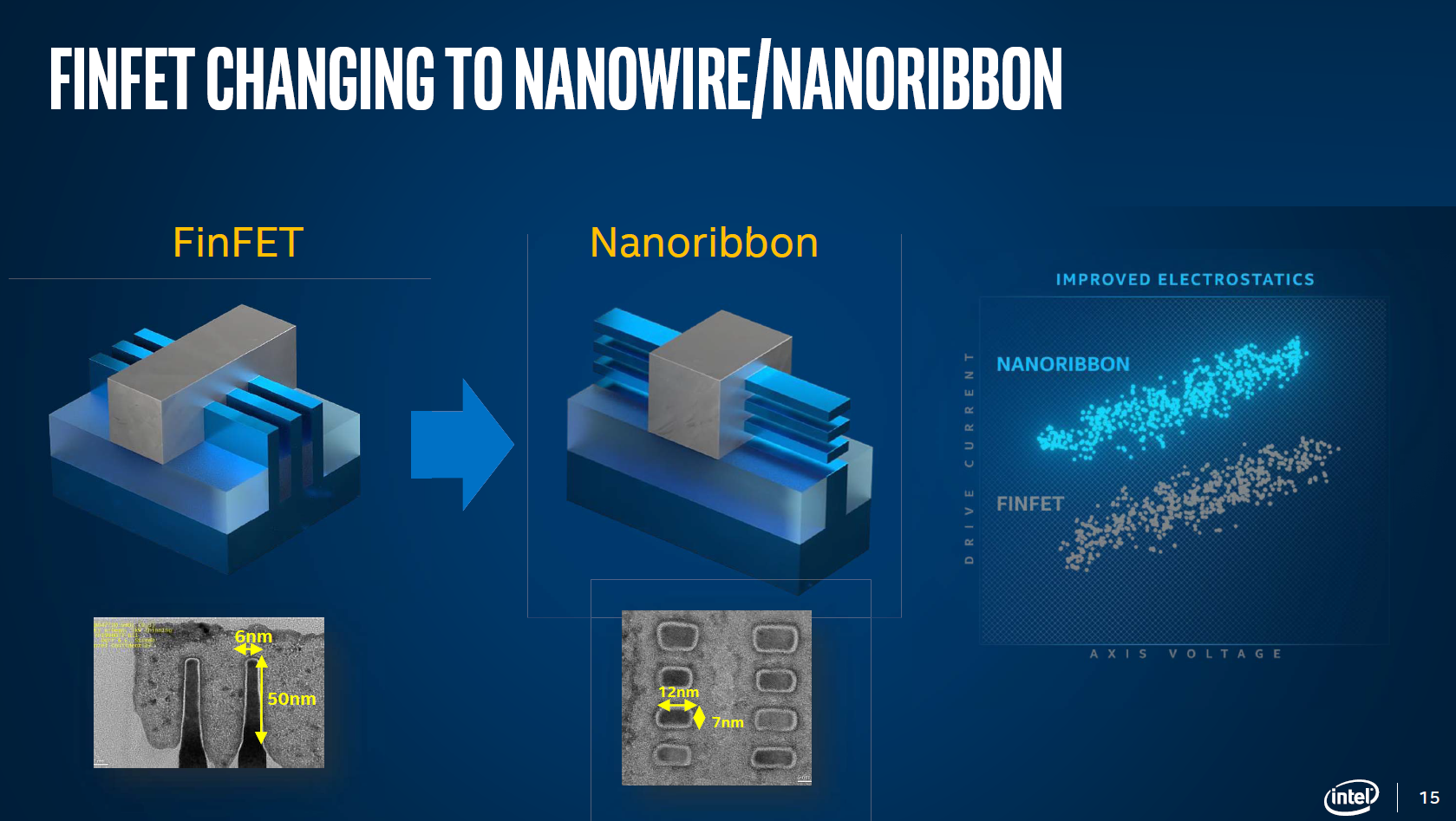

Conventional integrated circuits incorporate planar field effect transistors (FETs) in which current flows through a semiconducting channel between a source and a drain, in response to a voltage applied to a control gate. The semiconductor industry strives to obey Moore's law, which holds that each successive generation of integrated circuit devices shrinks to half its size and operates twice as fast. As device dimensions have shrunk below 100 nm, however, conventional silicon device geometries and materials have experienced difficulty maintaining switching speeds without incurring failures such as, for example, leaking current from the device into the semiconductor substrate. Several new technologies have emerged that allowed chip designers to continue shrinking gate lengths to 45 nm, 22 nm, and then as low as 14 nm. One particularly radical technology change entailed re-designing the structure of the FET from a planar device to a three-dimensional device in which the semiconducting channel was replaced by a fin that extends out from the plane of the substrate. In such a device, commonly referred to as a FinFET, the control gate wraps around three sides of the fin so as to influence current flow from three surfaces instead of one. The improved control achieved with a 3-D design results in faster switching performance and reduced current leakage. Building taller devices has also permitted increasing the device density within the same footprint that had previously been occupied by a planar FET. Examples of FinFET devices are described in further detail in U.S. Pat. No. 8,759,874 and U.S. Patent Publication 2014/0175554, assigned to the same assignee as the present patent application.

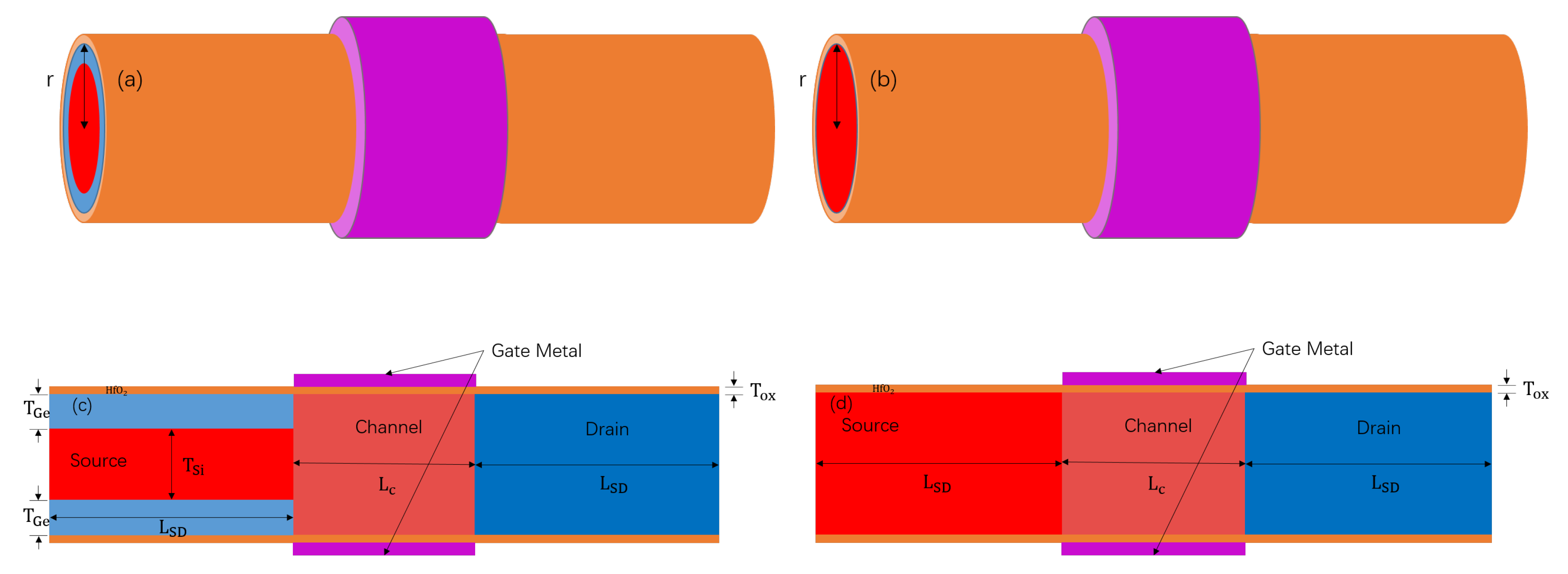

A vertical tunneling FET (TFET) provides low-power, high-speed switching performance for transistors having critical dimensions below 7 nm. The vertical TFET uses a gate-all-around (GAA) device architecture having a cylindrical structure that extends above the surface of a doped well formed in a silicon substrate.

The FinFET concept was further extended by developing a gate-all-around FET, or GAA FET, in which the gate fully wraps around the channel for maximum control of the current flow therein. In the GAA FET, the channel can take the form of a cylindrical nanowire that is isolated from the substrate, in contrast to the peninsular fin. In the GAA FET the cylindrical nanowire is surrounded by the gate oxide, and then by the gate. Existing GAA FETs are oriented horizontally, such that the nanowire extends in a direction that is substantially parallel to the surface of the semiconductor substrate. GAA FETs are described in, for example, U.S. Patent Publication No. 2013/0341596 to Chang et al., of IBM, and in U.S. Patent Publication No. 2015/0372104 to Liu et al., assigned to the same assignee as the present patent application.

As integrated circuits shrink with each technology generation, more power is needed to drive a larger number of transistors housed in a smaller volume. To prevent chips from overheating, and to conserve battery power, each generation of transistors is designed to operate at a lower voltage and to dissipate less power. In a conventional complementary metal-oxide-semiconductor (CMOS) field effect transistor, the source and drain are doped to have a same polarity, e.g., both positive, in a P-FET, or both negative, in an N-FET. When the gate voltage applied to the transistor, VG, exceeds a threshold voltage, VT, the device turns on and current flows through the channel. When the gate voltage applied to the transistor is below the threshold voltage, the drain current, ID, ideally is zero and the device is off. However, in reality, in the sub-threshold regime, there exists a small leakage current that is highly sensitive to the applied voltage. Over time, the leakage current drains charge from the power supply, e.g., a mobile phone battery or a computer battery, thus necessitating more frequent recharging. A change in gate voltage that is needed to reduce the sub-threshold leakage current by a factor of 10 is called the sub-threshold swing. It is desirable for the sub-threshold swing to be as small as possible. It is understood by those skilled in the art that MOSFETs have reached their lower limit of sub-threshold swing at 60 mV/decade. Thus, a different type of device is needed to further decrease the sub-threshold swing.

Tunneling field effect transistors (TFETs) are considered promising alternatives to conventional CMOS devices for use in future integrated circuits having low-voltage, low-power applications. Unlike a MOSFET, the source and drain of a TFET are doped to have opposite polarity. During operation of the TFET, charge carriers tunnel through a potential barrier rather than being energized to surmount the potential barrier, as occurs in a MOSFET. Because switching via tunneling requires less energy, TFETs are particularly useful in low-power applications such as mobile devices, for which battery lifetime is of utmost importance. Another reason TFETs provide enhanced switching performance for low-voltage operation is that TFETs have substantially smaller values of sub-threshold swing than MOSFETs.

A vertical TFET provides low-power, high-speed switching performance for transistors having critical dimensions below 7 nm. In one embodiment, the vertical TFET is implemented in silicon, using a gate-all-around (GAA) device architecture. The vertical GAA TFET is a linear, or 1-D, device in the form of a nanowire oriented transverse to planar front and back surfaces of the silicon substrate. The nanowire includes a lower drain region, a channel, and an upper source region, which are grown epitaxially from the doped well. The channel region is made of intrinsic silicon, while the source and drain regions are doped in-situ. An annular gate surrounds the channel region, capacitively controlling current flow through the channel from all sides. The source is electrically accessible via a front side contact, while the drain is accessed via a backside contact that provides low contact resistance and also serves as a heat sink.

Reliability of vertical TFET integrated circuits is enhanced by coupling the TFETs to electrostatic discharge (ESD) diodes. Both vertical and horizontal ESD diode configurations are described herein. ESD diodes provide protection for TFETs and other GAA transistors against high currents and voltages, especially in analog and I/O applications.

Fabrication of the vertical TFETs and ESD diodes as described herein is compatible with conventional CMOS manufacturing processes. Low-power operation allows the vertical TFET to provide a high current density, or “current per footprint” on a chip, compared with conventional planar transistors. The high current density allowed by these devices makes them good candidates for memory applications, e.g., for SRAM arrays.

In the drawings, identical reference numbers identify similar elements or acts. The sizes and relative positions of elements in the drawings are not necessarily drawn to scale.

FIG. 1 is a flow diagram showing steps in a method of fabricating a pair of n-type and p-type vertical GAA TFETs as illustrated in FIGS. 2-12, according to one embodiment described herein.

FIGS. 2-12 are cross-sectional views of the vertical GAA TFETs at successive steps during fabrication using the method shown in FIG. 1.

FIGS. 13-14 are cross-sectional views of alternative embodiments of completed n-type and p-type vertical GAA TFETs shown in FIG. 12, wherein each embodiment has a different contact configuration, as described herein.

FIG. 15 is a flow diagram showing steps in a method of fabricating a pair of vertical diodes as illustrated in FIGS. 16-18, according to a first embodiment as described herein.

FIGS. 16-18 are cross-sectional views of the pair of vertical diodes at successive steps during fabrication using the method shown in FIG. 15.

FIG. 19 is a cross-sectional view of a completed vertical diode, according to a second embodiment as described herein.

FIG. 20 is a flow diagram showing steps in an alternative method of fabricating vertical diodes and a horizontal diode, according to one embodiment described herein.

FIG. 21 is a cross-sectional view of a completed pair of vertical diodes and a horizontal diode fabricated using the method shown in FIG. 20.

In the following description, certain specific details are set forth in order to provide a thorough understanding of various aspects of the disclosed subject matter. However, the disclosed subject matter may be practiced without these specific details. In some instances, well-known structures and methods of semiconductor processing comprising embodiments of the subject matter disclosed herein have not been described in detail to avoid obscuring the descriptions of other aspects of the present disclosure.

Unless the context requires otherwise, throughout the specification and claims that follow, the word “comprise” and variations thereof, such as “comprises” and “comprising” are to be construed in an open, inclusive sense, that is, as “including, but not limited to.”

Reference throughout the specification to “one embodiment” or “an embodiment” means that a particular feature, structure, or characteristic described in connection with the embodiment is included in at least one embodiment. Thus, the appearance of the phrases “in one embodiment” or “in an embodiment” in various places throughout the specification are not necessarily all referring to the same aspect. Furthermore, the particular features, structures, or characteristics may be combined in any suitable manner in one or more aspects of the present disclosure.

Reference throughout the specification to integrated circuits is generally intended to include integrated circuit components built on semiconducting substrates, whether or not the components are coupled together into a circuit or able to be interconnected. Throughout the specification, the term “layer” is used in its broadest sense to include a thin film, a cap, or the like and one layer may be composed of multiple sub-layers. Throughout the specification, the terms “N-well” and “N-well region” are used synonymously in reference to negatively-doped regions of a semiconductor. Likewise, the terms “P-well” and “P-well region” are also used synonymously in reference to positively-doped regions of a semiconductor.

Reference throughout the specification to conventional thin film deposition techniques for depositing silicon nitride, silicon dioxide, metals, or similar materials include such processes as chemical vapor deposition (CVD), low-pressure chemical vapor deposition (LPCVD), metal organic chemical vapor deposition (MOCVD), plasma-enhanced chemical vapor deposition (PECVD), plasma vapor deposition (PVD), atomic layer deposition (ALD), molecular beam epitaxy (MBE), electroplating, electro-less plating, and the like. Specific embodiments are described herein with reference to examples of such processes. However, the present disclosure and the reference to certain deposition techniques should not be limited to those described. For example, in some circumstances, a description that references CVD may alternatively be done using PVD, or a description that specifies electroplating may alternatively be accomplished using electro-less plating. Furthermore, reference to conventional techniques of thin film formation may include growing a film in-situ. For example, in some embodiments, controlled growth of an oxide to a desired thickness can be achieved by exposing a silicon surface to oxygen gas or to moisture in a heated chamber.

Reference throughout the specification to conventional photolithography techniques, known in the art of semiconductor fabrication for patterning various thin films, includes a spin-expose-develop process sequence typically followed by an etch process. Alternatively or additionally, photoresist can also be used to pattern a hard mask (e.g., a silicon nitride hard mask), which, in turn, can be used to pattern an underlying film.

Reference throughout the specification to conventional etching techniques known in the art of semiconductor fabrication for selective removal of polysilicon, silicon nitride, silicon dioxide, metals, photoresist, polyimide, or similar materials includes such processes as wet chemical etching, reactive ion (plasma) etching (RIE), washing, wet cleaning, pre-cleaning, spray cleaning, chemical-mechanical planarization (CMP) and the like. Specific embodiments are described herein with reference to examples of such processes. However, the present disclosure and the reference to certain deposition techniques should not be limited to those described. In some instances, two such techniques may be interchangeable. For example, stripping photoresist may entail immersing a sample in a wet chemical bath or, alternatively, spraying wet chemicals directly onto the sample.

Specific embodiments are described herein with reference to vertical gate-all-around TFET devices that have been produced; however, the present disclosure and the reference to certain materials, dimensions, and the details and ordering of processing steps are exemplary and should not be limited to those shown.

Turning now to the figures, FIG. 1 shows steps in a method 100 of fabricating a pair of vertical GAA TFETs 182n,p, according to one embodiment. The completed GAA TFET devices produced by the method 100 are shown in FIG. 12. Alternative embodiments of the GAA TFET, formed by modifying the method 100, are shown in FIGS. 13-14. Each vertical GAA TFET is in the form of an epitaxially grown pillar having a doped lower drain region, a central channel region made of intrinsic silicon, and an upper source region doped to have a polarity opposite that of the lower drain region. The central channel region extends between the source and drain regions. A gate structure surrounds the channel region so as to influence current flow between the source and drain regions in response to an applied voltage. Steps in the method 100 are further illustrated by FIGS. 2-12, and described below.

At 102, an isolation region 132 is formed in a silicon substrate 130 to separate p-type and n-type devices that will subsequently be formed. The isolation region 132 incudes a liner 134 made of, for example, silicon nitride, and a silicon dioxide core 136, as shown in FIG. 2.

At 104, with reference to FIG. 3, a silicon substrate 130 having a <111> crystal orientation is doped to form an N-well 140 and a P-well 142 by ion implantation using a hard mask 138, as is well known in the art. The exemplary hard mask 138 is made of silicon dioxide (SiO2) having a thickness in the range of about 10 nm-50 nm. The hard mask 138 is grown or deposited over the surface of the silicon substrate 130, and is patterned with a first opening 139 to define the P-well 142, for example. Positive dopants such as boron ions are implanted into the silicon substrate 130 through the first opening 139 and then annealed to drive in the dopants to a selected depth 144. In one embodiment, the boron concentration is desirably within the range of about 1.0 E16 cm−3-5.0 E20 cm−3, targeted at 5.0 E19 cm−3. Then the hard mask 138 is stripped, re-formed, and patterned with a second opening 146 for the N-well 140. Negative dopants such as phosphorous ions or arsenic ions are then implanted into the silicon substrate 130 through the second opening 146, followed by annealing to drive in the negative dopants to the selected depth 144. In one embodiment, the n-dopant concentration is desirably within the range of about 1.0 E16 cm−3-3.0 E20 cm−3, targeted at 2.0 E19 cm−3. The first and second openings 139 and 146, respectively, can be the same size or different sizes, within a wide range of about 2 nm-200 nm.

At 106, epitaxial drain regions 150n and 150p are formed by epitaxial growth from the N-well and P-well regions 140 and 142 as shown in FIG. 4, extending in a transverse orientation to the silicon substrate 130. The hard mask 138 is stripped, re-formed, and re-patterned with a smaller opening 148n, for example. The drain region 150n is then grown epitaxially from a top surface of the N-well 140. The hard mask 138 is again stripped, re-formed, and re-patterned with a small opening 148p. The drain region 150p is then grown epitaxially from a top surface of the P-well 142. The drain regions 150n and 150p are grown to a height anywhere within the wide range of about 5 nm-500 nm, with doping occurring in-situ during the epitaxial growth. The order in which the n- and p-type structures are patterned and grown is exemplary as described above, and can be reversed.

At 108, nanowires 151n and 151p containing intrinsic silicon channels 152 and source regions 154n and 154p, respectively, are grown epitaxially from the drain regions 150n and 150p to complete formation of the pillars. First, cylindrical channels 152 made of intrinsic silicon are grown to a height within the range of 2 nm-100 nm. Then, a source region 154n made of indium arsenide (InAs), an n-type material, is selectively grown from the intrinsic silicon channel 152 that overlies the P-well 142 while a source region 154p made of a boron-SiGe compound (BSixGe(1-x)), a p-type material, is selectively grown from the intrinsic silicon channel 152 that overlies the N-well 140, as shown in FIG. 4. The source regions 154n and 154p are each grown to a thickness within the range of about 5 nm-500 nm. The epitaxial nanowires 151n and 151p, as grown, have widths 148p and 148n, respectively. Next, the epitaxial nanowires 151n and 151p are trimmed to a target critical dimension (CD) 156, as needed, as shown in FIG. 5 using a plasma etching process. The CD 156 can be defined using a silicon nitride hard mask, for example. In one embodiment, epitaxial growth of the regions 150n, 150p, 152, 154p, and 154n may occur inside patterned pillar-shaped holes formed in an insulating material, to provide support for the vertical nanowires 151n and 151p. The insulating material can include one or more layers, and the pillar-shaped holes may further include liners. The pillar-shaped holes may be used to define CD boundaries for the vertical nanowires 151n and 151p.

At 110, the epitaxial nanowires 151n and 151p are encapsulated by spin-coating a thick layer of benzocyclobutene (BCB) 158 to cover the epitaxial nanowires, and then performing a chemical-mechanical planarization (CMP) operation that stops on the InAs and BSixGe(1-x) source regions 154n and 154p, respectively.

At 112, the BCB encapsulant 158 is etched back to reveal the epitaxial nanowires 151n and 151p and top portions of the drain regions 150n and 150p, so that multi-layer gate structures 159 can be formed in contact with the exposed nanowires, as shown in FIG. 6, according to one embodiment. The multi-layer gate structures 159 include a dielectric sheath wrapped around the channel and a metal gate wrapped around the dielectric sheath. The etch-back process can be, for example, a plasma etch process that uses an O2—SF6 chemistry. Once the epitaxial nanowires are exposed, a gate oxide 160 is conformally deposited. The gate oxide 160 is desirably a high dielectric constant, or high-k, material of thickness 1 nm-10 nm, such as HfO2 or Al2O3, for example. Next, a work function material 162 of thickness 1 nm-20 nm is conformally deposited, followed by a gate metal 164 of thickness 10 nm-200 nm. The gate metal 164 and the work function material 162 can be, for example, copper (Cu), aluminum (Al), tungsten (W), platinum (Pt), gold (Au), titanium nitride (TiN), tantalum nitride (TaN), titanium carbon (TiC), titanium-tungsten (TiWx), or combinations thereof. Regions of the gate stack located between adjacent nanowires are then etched away as shown in FIG. 7, while regions of the gate stack outside the epitaxial nanowires remain to form gate contact landing pads 168.

At 114, the gate structures 159 are encapsulated. In one embodiment, encapsulation is accomplished by spin coating a second BCB layer 166, followed by a CMP process that is targeted to stop when a selected BCB thickness has been reached, above the metal gate structures 159. Alternatively, the planarization process can stop on the metal gate structures 159.

At 116, the second BCB layer 166 is etched back to reveal portions of the metal gate structures 159 covering the source regions 154n, 154p to a level in the range of about 1 nm-300 nm above the intrinsic silicon channel 152 to expose the gate metal 164. Then, the gate metal 164 and the work function material 162 are etched away to reveal the gate oxide 160 covering the source regions, thus leaving behind completed gates 170 surrounding the intrinsic silicon channel regions.

At 118, epitaxial nanowires 151p,n are encapsulated. In one embodiment, encapsulation is accomplished by spin coating a third BCB layer 172, followed by a CMP process that is targeted to stop when a selected BCB thickness has been reached, above the gate structures 159.

At 120, the third BCB layer 172 and the gate oxide 160 are etched back to a height 173 above a top surface of the gate metal 164, to reveal the top 3 nm-300 nm of the InAs and BSixGe(1-x) source regions 154n,p, as shown in FIGS. 9-12.

At 122, source regions 154n, p are encapsulated. In one embodiment, encapsulation is accomplished by spin coating a fourth BCB layer 174, followed by a CMP process that is targeted to stop when a selected BCB thickness has been reached, above the gate structures 159. Alternatively, an oxide deposited using a high density plasma (HDP) process can be used in place of the fourth BCB layer 174.

At 124, contacts are made to the source regions. In one embodiment, a dual damascene process is used to form front side source contacts 182 to the epitaxial nanowire and a metal interconnect layer, while backside contacts 184 are made to the epitaxial drain regions 150n,p via the implant-doped well regions. First, dual damascene trenches 176 are etched in the fourth BCB layer 174, as well as contact holes surrounding the source regions 154n,p, as shown in FIG. 10. Then the source regions 154n,p can be reacted with metal to form a silicide e.g., TiSi, NiSiPt, or a dual silicide such as Pt, Ir for the p-type source 154p, or Er, Yb for the n-type source 154n prior to filling the trenches and contact holes using established methods familiar to those skilled in the art of damascene processing. The metal fill desirably includes a liner made of, for example, TiN or TiC. The metal is then planarized to stop on the fourth BCB layer, as shown in FIG. 11. Finally, metal contacts of thickness 5 nm-50 μm are made to the backside of the wafer to contact the N-well 140 and the P-well 142, as shown in FIG. 12.

FIG. 13 shows a second embodiment of the vertical GAA TFET in which additional spacers are wrapped around the pillars between the gate structures 170 and the source and drain regions. A first spacer 185 is formed between the gate structures 170 and the source regions 154n,p, and a second spacer 186 is formed between the gate structures 170 and the drain regions 140, 142. The spacers 185, 186 can be made of SiN or SiC, for example.

FIG. 14 shows a third embodiment of the vertical GAA TFET that features etched source contacts 190 in place of dual damascene contacts 182. The source contacts 190 differ from the dual damascene contacts 182 in that the source contacts 190 are formed by a subtractive etching process as opposed to forming and filling a trench, which is an additive process. Although either method can be used to form contacts to the source terminals of the GAA TFET, the front side source contacts 182 formed by the dual damascene process may offer lower contact resistance and a more flexible wire connection.

FIG. 15 shows steps in a method 200 of fabricating a vertical diode, according to one embodiment. The vertical diode can provide electrostatic discharge (ESD) protection for the vertical GAA TFET described above, to improve reliability. One advantage of the vertical diode is its small footprint, which is particularly useful in supporting GAA transistors used to form digital SRAM and DRAM arrays. The method 200 is further illustrated by FIGS. 16-19, and described below. The ESD diode fabrication process can be performed at the same time as formation of the vertical GAA TFET and therefore the same reference numerals are used in the following description of the ESD diode formation, wherever possible.

At 202, the silicon substrate 130 is implanted with dopants through openings in an implant hard mask 138 on a top side or surface 129 of the substrate 130. In one embodiment, the implant hard mask 138 is a 10 nm-50 nm thick layer of SiO2. An opening in the implant hard mask 138, in the range of about 2 nm-200 nm can be patterned using an RIE process. Positive ions, such as boron, can then be implanted in the substrate to form a p-doped region, or P-well 142, shown in FIG. 16, having a dopant concentration of 1.0 E16 cm−3-1.0 E 20 cm−3. The P-well 142 is formed between a first portion 130-1 of the substrate 130 and a second portion 130-2 of the substrate 130.

At 204, an n-doped vertical nanowire 154 having a top end 157 and a bottom end 159, shown in FIG. 16, is formed by epitaxial growth from a top side or surface 141 of the p-doped region 142. In one embodiment, the vertical nanowire 154 is made of indium arsenide (InAs) having a diameter anywhere in the range of about 2 nm-200 nm and a height anywhere in the range of about 8 nm-800 nm. Growth of the vertical nanowire 154 can be performed in a metal organic chemical vapor deposition (MOCVD) chamber using a trimethyl-indium (TMIn) source and a tertiarybutyl-arsine molar flow of 0.7 μMol/min-12.6 μMol/min, at a reactor pressure of 60 Torr, and a temperature between 400 C and 600 C. Negative doping of the vertical nanowire 154 can be achieved in-situ by injecting disilane gas (Si2H6) during the epitaxial growth process at Si2H6/TMIn ratios of 10−6-10−2. The junction of the bottom end 159 of the n-doped vertical nanowire 154 and the top side or surface 141 of the p-doped region 142 form a p-n diode 182n.

At 206, the vertical nanowire 154 is encapsulated. In one embodiment, an encapsulant 174 is a layer of benzocyclobutene (BCB) that is spin-coated to cover the p-n diode 182n, and a CMP process is then used to planarize the encapsulant 174 to a target thickness above the vertical nanowire 154.

At 208, a front side contact is formed to the vertical nanowire 154 using a dual damascene process similar to that shown in FIGS. 10-11 and described above, in which a contact via and a metal line trench having a T-shaped profile are etched in the encapsulant 174, and then the contact via and the metal line trench are filled with metal. The metal fill includes a liner 178 such as TiN, Ti/TiN, Ta, or TaN that surrounds a top portion 155 of the vertical nanowire 154, and a bulk metal 180 such as W, Al, Cu, or Au that has a bottom portion or region 181 and a top portion or region 183. A silicidation process may be performed is formed at the contact surfaces of the vertical nanowire 154 to further reduce contact resistance as described above. The bulk metal is then planarized to stop on the BCB layer.

At 210, a backside contact 184 is made on a bottom side or surface 131 of the substrate 130 to a bottom side or surface 143 of the P-well 142, similar to those shown in FIGS. 12-14 and described above.

FIG. 18 shows a pair of vertical diodes, including the p-n diode 182n described above, and a reciprocal p-n diode 182p. Whereas the p-n diode 182n includes a P-well and an n-doped vertical nanowire, the p-n diode 182p includes an N-well and a p-doped vertical nanowire. The two diodes are separated by an isolation region 132 that can be formed in the usual way, prior to doping the silicon substrate 130. The diodes 182p and 182n have separate backside contacts 184p and 184n. Optional spacers 186 may be formed below the contact vias, prior to the encapsulation step 206. The spacers 186 can be made of SiC or SiCNH, for example.

FIG. 19 shows an alternative contact 190 to the vertical p-n diode 182n. The alternative contact 190 is formed by recessing the encapsulant 174 down to a level below the top of the vertical nanowire 154, and then performing metallization using a subtractive process instead of a dual damascene process. The subtractive process entails conformally depositing a layer of metal and patterning and etching the metal, producing an inverted V-shaped profile. The alternative contact 190 is better suited to metal materials such as AlCu as opposed to Cu, which is difficult to etch. Following formation of the alternative contact 190, a top ILD layer 192 is deposited and planarized to stop on the inverted V-shaped contact 190.

FIG. 20 shows steps in a method 230 of fabricating an integrated horizontal p-n junction diode 222, according to one embodiment shown in FIG. 21.

At 232, the silicon substrate 130 is implanted with an N-well 140 as described above in step 104.

At 234, the silicon substrate 130 is implanted with a P-well 142 adjacent to the N-well 140 as described above in step 104, except that the P-well 142 partially overlaps the N-well 140 at 224. The overlap can be accomplished via mask alignment or by using a tilted implantation process. The horizontal p-n junction diode 222 thus formed is useful in protecting GAA transistors used in analog and I/O circuits that sustain high currents and voltages.

At 236, an insulating layer is formed, for example, the BCB encapsulant 158, using a process similar to the one described above in step 110.

Gallium Arsenide Transistor

At 238, front side damascene contacts are made to the N-well 140 and the P-well 142, using a process similar to the one described above in step 124, wherein the contacts have T-shaped profiles.

At 240, the backside contact 184 is formed to the silicon substrate 130.

It will be appreciated that, although specific embodiments of the present disclosure are described herein for purposes of illustration, various modifications may be made without departing from the spirit and scope of the present disclosure. Accordingly, the present disclosure is not limited except as by the appended claims.

Gaa Fet Process Flow

These and other changes can be made to the embodiments in light of the above-detailed description. In general, in the following claims, the terms used should not be construed to limit the claims to the specific embodiments disclosed in the specification and the claims, but should be construed to include all possible embodiments along with the full scope of equivalents to which such claims are entitled. Accordingly, the claims are not limited by the disclosure.

Gaafet Transistor

The various embodiments described above can be combined to provide further embodiments. All of the U.S. patents, U.S. patent application publications, U.S. patent applications, foreign patents, foreign patent applications and non-patent publications referred to in this specification and/or listed in the Application Data Sheet are incorporated herein by reference, in their entirety. Aspects of the embodiments can be modified, if necessary to employ concepts of the various patents, applications and publications to provide yet further embodiments.

Virtual Conference Center

Day 1 April 8th

- TTUA1-1 9:00 Skin-Inspired Organic Electronics

Zhenan Bao, Stanford University, California, USA - TTUA1-2 10:10 2D material based flexible and wearable electronics

Jong-Hyun Ahn, Yonsei University, Seoul, Korea - TTUA1-3 11:20 A Metal-Oxide Transistor Technology for Flexible Electronics

Man Wong, Hong Kong University of Science and Technology, Hong Kong, China

- TTUA1-1 9:00 Skin-Inspired Organic Electronics

- TTUA2-1 9:00 6G: Towards a More Connected and Sustainable World

Mohamed-Slim Alouini, King Abdullah University of Science and Technology, Saudi Arabia - TTUA2-2 10:10 Topological Spintronics for Low Energy Dissipation

Kang L. Wang, University of California, Los Angeles, USA - TTUA2-3 11:20 In- and Near-Memory Computing Using 2D/3D Resistive Memories

Philip Wong, Stanford University, California, USA

- TTUA2-1 9:00 6G: Towards a More Connected and Sustainable World

- 09:00—09:05 Welcome EDTM & HIR

- 09:05—09:30 HIR Overview: William Chen, WR Bottoms & Ravi Mahajun

- 09:30—09:55 Automotive Electronics: Urmi Ray & Rich Rice

- 09:55—10:20 SiP & Module: R. Aschenbrenner, Klaus Pressel, Erik Jung

- 10:20—10:45 MEMS & Sensor Integration: Shafi Saiyed & MaryAnn Mahar

- 10:45—11:10 Simulation & Co-Design: Christopher Bailey & Xuejun Fan

- 11:10—11:35 Reliability: Abhijit Dasgupta, Richard Rao, Shubhana Sahasrabudha

- 11:35—12:00 Integrated Power Electronics: Patrick McCluskey & Douglas Hopkins

- 12:00—12:30 Panel Session: Moderators: Subramanian Iyer & William Chen

- STUP1-1 14:00 Computing-in-memory design for general neural networks inference

Shaodi Wang, Founder/CEO of WITINMEM, Beijing, China - STUP1-2 15:10 Emerging Device Technologies for Neuromorphic Computing and Machine Learning

Damien Querlioz, Université Paris-Saclay, CNRS, France - STUP1-3 16:20 RRAM Based Computing-In-Memory

Qi Xiang, CTO of Xiamen Industrial Technology Research Institute Co., LTD, China

- STUP1-1 14:00 Computing-in-memory design for general neural networks inference

- STUP2-1 14:00 Cryo-CMOS for Quantum Computing

Edoardo Charbon, EPFL, Switzerland - STUP2-2 15:10 Understanding quantum computing by quantum algorithms

Lvzhou Li, Sun Yat-sen University, China - STUP2-3 16:20 Quantum computing using superconducting quantum coherence devices

Yuxi Liu, Tsinghua University, China

- STUP2-1 14:00 Cryo-CMOS for Quantum Computing

- STUP3-1 14:00 Layer transfer technology of post-Si materials for monolithic 3D integration

Tatsuro Maeda, National Institute of Advanced Industrial Science and Technology, Japan - STUP3-2 15:10 Device/Process Technology Challenges for CMOS System Evolution

Digh Hisamoto, Hitachi, Japan - STUP3-3 16:20 EUV lithography and its applications to logic and memory devices

Wei-Min Gao, ASML China

- STUP3-1 14:00 Layer transfer technology of post-Si materials for monolithic 3D integration

- STUP4-1 14:00 Integration with GaN-on-Si Power HEMT platform

Kevin J. Chen, Hong Kong University of Science and Technology, Hong Kong, China - STUP4-2 15:10 Energy efficient power switches with Gallium Nitride technology

Srabanti Chowdhury, Stanford University, California, USA - STUP4-3 16:20 Element Technology for Next Generation High- to Ultra-High Voltage SiC Power Device

Yoshiyuki Yonezawa, AIST, Japan

- STUP4-1 14:00 Integration with GaN-on-Si Power HEMT platform

Day 2 April 9th

09:30—10:15 Plenary 1: Creating Values through Innovations on Mature Nodes of Technologies of Integrated Circuits

Haijun Zhao, Co-CEO, SMIC., PR China10:15—11:00 Plenary 2: How to build a camera with highest resolution: a photonics perspective

Professor Xiang Zhang, President and Vice-Chancellor

The University of Hong Kong, Hong Kong SAR, PR China11:00—11:45 Plenary 3: The power of image sensors for innovation

Teruo Hirayama, Executive Chief Engineer, Sony Corp., Japan- WE1P1-1 13:30 Pushing the Limit of Lithography for Patterning Two-Dimensional Lattices in III-V Semiconductor Quantum Wells (Invited talk)

N.A. Franchina Vergel1, C. Post2, F. Vaurette1, Y. Lambert1, D. Yarekha1, C. Coinon1, G. Fleury3, T.S. Kulmala4, T. Xu5, L. Desplanque1, X. Wallart1, D. Vanmaekelbergh2, C. Delerue1, B. Grandidier1;1Univ. Lille, France,2Utrecht University, The Netherlands, 3Univ. Bordeaux, France,4Heidelberg Instruments, Switzerland,5Shanghai University, China - WE1P1-2 13:50 Graphene Synthesis: From Single Crystalline Wafer to Edge Specific Nano-Ribbon (Invited talk)

Zengfeng Di, Tianru Wu, Haomin, Wang, Qingkai Yu, Xiaoming Xie; Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China - WE1P1-3 14:10 Artificial Heterostructures Enabled by Remote Epitaxy (Invited talk)

Jeehwan Kim; Massachusetts Institute of Technology, USA - WE1P1-4 14:30

Yan Liu, Yue Peng, Genquan Han; Xidian University, China - WE1P1-5 14:50 Silicon Nanocrystals: Fabrication, Physical Properties and Applications (Invited talk)

Ilya Sychugov; KTH Royal Institute of Technology, Sweden

- WE1P1-1 13:30 Pushing the Limit of Lithography for Patterning Two-Dimensional Lattices in III-V Semiconductor Quantum Wells (Invited talk)

- WE1P2-1 13:30 Hot Carrier Degradation in Classical and Emerging Logic and Power Electronic Devices: Rethinking Reliability for Next-Generation Electronics (Invited talk)

Muhammad Ashraful Alam, Bikram Kishore Mahajan, Yen-Pu Chen; Purdue University, USA - WE1P2-2 13:50 Hot-Carrier-Induced Reliability Concerns for Lateral DMOS Transistors with Split-STI Structures

Li Lu1, Ran Ye1, Siyang Liu1, Zhibo Yin1, Yuanchang Sang1, Weifeng Sun1, Wei Su2, Feng Lin2, Shulang Ma2, Yuwei Liu2; 1Southeast University,China, 2CSMC Technologies Corporation, China - WE1P2-3 14:10 Identifying Relaxation and Random Telegraph Noises in Filamentary Analog RRAM for Neuromorphic Computing

Qi Hu1, Bin Gao1, Jianshi Tang1, Zhenqi Hao1, Peng Yao1, Yudeng Lin1, Yue Xi1, Meiran Zhao1, Jiezhi Chen2, He Qian1,Huaqiang Wu1; 1Tsinghua University, China, 2Shandong University, China - WE1P2-4 14:30 Nonlinear Weight Quantification for Mitigating Read Disturb Effect on Multilevel RRAM-Based Neural Network

Lindong Wu, Zongwei Wang , Zhizhen Yu, Yabo Qin, Qingyu Chen, Yimao Cai , Ru Huang; Peking University, China - WE1P2-5 14:50 Predicted static fatigue lifetime of silica optical interconnects: application of Boltzmann-Arrhenius-Zhurkov (BAZ) model (Invited talk)

Ephraim Suhir; Portland State University, USA

- WE1P2-1 13:30 Hot Carrier Degradation in Classical and Emerging Logic and Power Electronic Devices: Rethinking Reliability for Next-Generation Electronics (Invited talk)

- WE1P3-1 13:30 Heterogeneous Integration for Silicon Photonic Systems: Challenges and Approaches (Invited talk)

John M. Dallesasse, John A. Carlson, Manaav Ganjoo, Leah Espenhahn; University of Illinois at Urbana-Champaign, USA - WE1P3-2 13:50 Effect of Leveler on Electrical Resistance and Microstructural of Electroplated Copper After Heat Treatment

Lingyue Tan, Silin Han, Shuhui Chen, Chu Liang, Yunwen Wu, Huiqin Ling, Ming Li, Tao Hang; Shanghai Jiao Tong University, China - WE1P3-3 14:10 Heterogenous Integration of InP DHBT and Si CMOS by 30μm Pitch Au-In Microbumps

LiShu Wu1,2, JiaYun Dai1, Cheng Wei1, YueChan Kong1, TangShen Chen1, Tong Zhang2; 1Science and Technology on Monolithic Integrated Circuits and Modules Laboratory Nanjing Electronic Devices Institute, China, 2Southeast University, China - WE1P3-4 14:30 Simulation of fast room-temperature bonding by mechanical interlock structure applied for 3D integration

Ziyu Liu, Yaomin Gong, Lin Chen, Qingqing Sun, David Wei Zhang; Fudan University, China - WE1P3-5 14:50 Low Temperature Packaging for Ion-Sensitive Organic Field Effect Transistor

Yixiao Tang, Wei Tang, Yukun Huang, Yawen Song, Bang Ouyang, Xiaojun Guo; Shanghai Jiao Tong University, China

- WE1P3-1 13:30 Heterogeneous Integration for Silicon Photonic Systems: Challenges and Approaches (Invited talk)

- WE1P4-1 13:30 Ferroelectric field-effect transistors for the next-generation storage (Invited talk)

Cheol Seong Hwang; Seoul National University,Korea - WE1P4-2 13:50 Toward Energy-efficient, Cost-effective, and Variation-aware In-memory Computing for Deep Learning Acceleration (Invited talk)

Tuo-Hung Hou; National Chiao Tung University, China - WE1P4-3 14:10 Design Limits of In-Memory Computing: Beyond the Crossbar (Invited talk)

Gokul Krishnan1, Jubin Hazra2, Maximilian Liehr2, Xiaocong Du1, Karsten Beckmann2, Rajiv V. Joshi3, Nathaniel C. Cady2, Yu Cao1; 1Arizona State University,USA, 2State University of New York Polytechnic Institute,USA, 3IBM T. J. Watson Research Center Yorktown Heights,USA - WE1P4-4 14:30 Three-Orders Improvement of Endurance in Hafina Based MFS Capacitor Through CF4 Plasma Pre-Treatment

Shuxian Lv1, 2, Yan Wang1, 2, Zhaomeng Gao1, 2, Zhiwei Dang1, 2, Pengfei Jiang1, 2, Peng Yuan1,2, Qing Luo1, 2, Shengjie Zhao1, Hangbing Lv1, 2; 1Institute of Microelectronics of Chinese Academy of Sciences, China; 2University of Chinese Academy of Sciences, China - WE1P4-5 14:50 A RRAM Based Max-Pooling Scheme for Convolutional Neural Network

Yaotian Ling, Zongwei Wang, Yunfan Yang, Zhizhen Yu, Qilin Zheng, Yabo Qin, Yimao Cai, Ru Huang; Peking University, China

- WE1P4-1 13:30 Ferroelectric field-effect transistors for the next-generation storage (Invited talk)

- WE2P1-1 15:30 Piezoelectric Micromachined Ultrasonic Transducers for Range-Finding Applications (Invited talk)

David A. Horsley1,2, Richard J. Przybyla1, Stefon E. Shelton1, Fabian T. Goericke1, Benjamin E. Eovino1, Michael Alex1 , John Logan1; 1Chirp Microsystems Corporation,USA, 2University of California, Davis, USA - WE2P1-2 15:50 Biaxially-Stretchable Kirigami-Patterned Mesh Structures for Motion Artifact-Free Wearable Devices (Invited talk)

Hyo Chan Lee1, Ezekiel Y. Hsieh1,SungWoo Nam1,2; 1Department of Mechanical Science and Engineering, University of Illinois at Urbana – Champaign, USA, 2Department of Materials Science and Engineering, University of Illinois at Urbana – Champaign, USA - WE2P1-3 16:10 Thermal Infrared Detector Sparse Array for NASA Planetary Applications (Invited talk)

M. Bulut Coskun1, Mina Rais-Zadeh1,2; 1California Institute of Technology,USA, 2University of Michigan, Ann Arbor, USA - WE2P1-4 16:30 Double-Deck Metal Solenoids 3D Integrated in Silicon Wafer for Kinetic Energy Harvester

Nianying Wang1,2,3, Ruofeng Han1,3, Changnan Chen1,3, Jiebin Gu1,3, and Xinxin Li1,2,3; 1Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, China, 2ShanghaiTech University, China, 3University of Chinese Academy of Sciences, China - WE2P1-5 16:50 A Novel Piston-Like Piezoelectric Micromachined Ultrasonic Transducer Based on Mass Loading Effect

Lei Wang,Jie Zhou, Wei Zhu, Zhipeng Wu, Wenjuan Liu, Chengliang Sun; Institute of Technological Sciences, China

- WE2P1-1 15:30 Piezoelectric Micromachined Ultrasonic Transducers for Range-Finding Applications (Invited talk)

- WE2P2-1 15:30 Analog Switches Based on Boron Nitride Memristors for Application in 5G and Terahertz Communication Systems (Invited talk)

Myungsoo Kim1, Emiliano Pallecchi2, Guillaume Ducournau2, Henri Happy2, Deji Akinwande1; 1University of Texas at Austin, USA, 2 University of Lille, France - WE2P2-2 15:50 Photonic Machine Intelligence: Photonic Tensor Core and Nonvolatile Memories (Invited talk)

Volker J. Sorger; George Washington University, USA - WE2P2-3 16:10 Efficient Silicon Photonic Waveguide Switches for Chip-Scale Beam Steering Applications (Invited talk)

Li-Yuan Chiang1, Chun-Ta Wang2, Steve Pappert1, Paul K. L. Yu1; 1University of California San Diego, USA, 2National Sun Yat-Sen University, China - WE2P2-4 16:30 A Design of Horizontal Perovskite Nanowire LED for Better Light Extraction

Qianpeng Zhang1,2, Yuanjing Lin3, Xiaofei Sun1, Bryan Cao1, Haoning Tang,4, Zhiyong Fan1,2; 1The Hong Kong University of Science and Technology, China, 2HKUST-Shenzhen Research Institute, China, 3Southern University - WE2P2-5 16:50 Loss Compensation Symmetry for TE Modes of Asymmetrical Optical Coupler with Gain and Loss

Anton Hlushchenko1,2, Vitalii Shcherbinin2, Denis Novitsky3, Vladimir Tuz1; 1Jilin University, China, 2Institute of Physics and Technology of NASU, Ukraine, 3NASB, Belarus

- WE2P2-1 15:30 Analog Switches Based on Boron Nitride Memristors for Application in 5G and Terahertz Communication Systems (Invited talk)

- WE2P3-1 15:30 All 2D Heterostructure Tunnel Field Effect Transistors (Invited talk)

Kosuke Nagashio; University of Tokyo, Japan - WE2P3-2 15:50 ALD Encapsulation of CVD WS2 for Stable and High-Performance FET Devices (Invited talk)

Xiangyu Wu, Dennis Lin, Daire Cott, Jean-Francois de Marneffe, Benjamin Groven, Stephanie Sergeant, Yuanyuan Shi, Quentin Smets, Surajit Sutar, Inge Asselberghs, Iuliana Radu; IMEC, Belgium - WE2P3-3 16:10 Epitaxial Growth of Single-Crystal Two-Dimensional Materials for Electronic Applications (Invited talk)

Areej Aljarb1,2, Vincent Tung1, Lain-Jong Li1,3; 1KAUST Solar Centre, Kingdom of Saudi Arabia, 2King Abdulaziz University, Kingdom of Saudi Arabia, 3 TSMC Taiwan - WE2P3-4 16:30 A Compact Model for Transition Metal Dichalcogenide Field Effect Transistors with Effects of Interface Traps

Yifei Xu, Weisheng Li, Dongxu Fan, Yi Shi, Hao Qiu, Xinran Wang; National Laboratory of Solid State Microstructures, School of Electronic Science and Engineering and Collaborative Innovation Center of Advanced Microstructures, Nanjing University, Nanjing, China - WE2P3-5 16:50 Reliability of Ultrathin High-k Dielectrics on 2D Semiconductors

Zhihao Yu1,2, Hongkai Ning2, Weisheng Li2 , Lei Liu2 , Wanqing Meng2 , Zhongzhong Luo2 , Songhua Cai3, Taotao Li2, Peng Wang3 , Yi Shi2 , Yong Xu1 , Xinran Wang2; 1Nanjing University of Posts and Telecommunications, China, 2School of Electronic Science and Engineering, Nanjing University, China, 3College of Engineering and Applied Sciences, Nanjing University, China

- WE2P3-1 15:30 All 2D Heterostructure Tunnel Field Effect Transistors (Invited talk)

- WE2P4-1 15:30 The Case for Ferroelectrics in Future Memory Devices (Invited talk)

Thomas Mikolajick1,2, Uwe Schroeder1, Stefan Slesazeck1;1NaMLab gGmbH, Germany, 2IHM, Germany - WE2P4-2 15:50 A Multiscale Statistical Evaluation of DRAM Variable Retention Time (Invited talk)

Plamen Asenov1 , Salvatore M. Amoroso1 , Jaehyun Lee1 , Fabiano Corsetti4 , Pieter Vancraeyveld4 , Søren Smidstrup4 ,Xi-Wei Lin3 ,Victor Moroz3; 1Synopsys, Scotland, 2Synopsys, Denmark, 3Synopsys, USA - WE2P4-3 16:10 3D-NAND cell challenges to enable high density and high performance devices (Invited talk)

Tecla Ghilardi; Micron - WE2P4-4 16:30 Performance Boost of p-MOSFET with Al-Incorporated HfSiOx in DRAM Periphery Transistor Application

Xingsong Su, Kang You, Mengmeng Yang, Juanjuan Huang, Wei Yang, Weiping Bai, Jie Bai, Er-xuan Ping; Changxin Memory Technologies, Inc, China - WE2P4-5 16:50 Cryogenic Operation of 3D Flash Memory for New Applications and Bit Cost Scaling with 6-Bit per Cell (HLC) and Beyond

Yuta Aiba, Hitomi Tanaka, Takashi Maeda, Keiichi Sawa, Fumie Kikushima, Masayuki Miura, Toshio Fujisawa, Mie Matsuo, Tomoya Sanuki; Kioxia Corporation, Japan

- WE2P4-1 15:30 The Case for Ferroelectrics in Future Memory Devices (Invited talk)

Day 3 April 10th

09:00—09:45 Plenary 4: Thin Film Transistor Architectures for Advanced Analog Signal Processing

Prof. Arokia Nathan, University of Cambridge, UK09:45—10:30 Plenary 5: Ferroelectric-based device: revived as a low-power technology booster for diverse applications

Prof. Ru Huang, Peking University, China10:30—11:15 Plenary 6: Ubiquitous Computing Drives Future Semiconductor Technology

Dr. Jeff Xu, HiSilicon Research, China- TH1A1-1 11:30 Smart Cut SiC Substrates for Manufacturing of High Quality Power Devices (Invited talk)

Walter Schwarzenbach; SOITEC, France - TH1A1-2 11:50 Directed Self-Assembly of Block Copolymers for Microelectronic Manufacturing (Invited talk)

Shisheng Xiong; Fudan University, China - TH1A1-3 12:10 Nanolithography to Beat the Diffraction Limit Using Ultrafast Laser (Invited talk)

Xuanming Duan; Jinan University, China

- TH1A1-1 11:30 Smart Cut SiC Substrates for Manufacturing of High Quality Power Devices (Invited talk)

- TH1A2-1 11:30 Flexible Semiconductor Device Technologies (Invited talk)

Huilong Zhang, Tzu-Hsuan Chang, Seunghwan Min, Zhenqiang Ma; University of Wisconsin-Madison, USA - TH1A2-2 11:50 Personalized Medicinal Platform (Invited talk)

Muhammad M. Hussain; King Abdullah University of Science and Technology, Saudi Arabia - TH1A2-3 12:10 Low-Voltage Synaptic Transistor Based on Polyvinylpyrrolidone Composite Electrolyte for Humidity Sensing

Wenhui Fu1, Jiang Dongliang1 , He Liangchun1 ,Yang Yaohua1 , Chen Qi1 , Zhang Jianhua2, Li Jun1; 1Shanghai University, China, 2Ministry of Education, Shanghai University, China

- TH1A2-1 11:30 Flexible Semiconductor Device Technologies (Invited talk)

- TH1A3-1 11:30 A BEOL Compatible, 2-Terminals, Ferroelectric Analog Non-Volatile Memory

Laura Bégon-Lours, Mattia Halter, Diana Dávila Pineda, Youri Popoff, Valeria Bragaglia, Antonio La Porta, Daniel Jubin, Jean Fompeyrine, Bert Jan Offrein; IBM Zurich Research Laboratory, Switzerland - TH1A3-2 11:50 A Novel Leaky-FeFET Based True Random Number Generator with Ultralow Hardware Cost for Neuromorphic Application

Tianyi Liu1 , Jin Luo1 , Xinming Wei1 ,Qianqian Huang1,2 , Ru Huang1,2; 1 Peking University, China, 2National Key Laboratory of Science and Technology on Micro/Nano Fabrication, China - TH1A3-3 12:10 Hf1-xZrxO2 Based Bipolar Selector with High Uniformity and High Selectivity for Large-Scale Integration of Memristor Crossbars

Caidie Cheng1,2, Keqin Liu2 , Bingjie Dang2 , Liying Xu2 , Zhen Yang2 , Xiaoqin Yan1, Yuchao Yang2, Ru Huang2; 1University of Science and Technology Beijing, China, 2Peking University, China

- TH1A3-1 11:30 A BEOL Compatible, 2-Terminals, Ferroelectric Analog Non-Volatile Memory

- TH1A4-1 11:30 Silicon Nanophotonic Devices for On-chip Optical Modulation and Switching (Invited talk)

Daoxin Dai , Lijia Song ,Bingchen Pan; Zhejiang University, China - TH1A4-2 11:50 Purcell effect and lasing from quantum dots in a topological photonic crystal nanocavity (Invited talk)

Xin Xie1,2, Weixuan Zhang3,4, Xiaowu He5 , Huiming Hao5 , Haiqiao Ni5 , Zhichuan Niu5 , Xiangdong Zhang3,4, Xiulai Xu1,2,6; 1Institute of Physics, Chinese Academy of Sciences, China, 2CAS Center for Excellence in Topological Quantum Computation and School of Physical Sciences, University of Chinese Academy of Sciences, China, 3School of Physics, Beijing Institute of Technology, China, 4School of Physics, Beijing Institute of Technology, China, 5Institute of Semiconductors Chinese Academy of Sciences, China, 6Songshan Lake Materials Laboratory, China - TH1A4-3 12:10 Manufacturing of State-of-The-Art InP-Based Photonic Integrated Circuits (Invited talk)

Fred Kish; NCSU/Infinera

- TH1A4-1 11:30 Silicon Nanophotonic Devices for On-chip Optical Modulation and Switching (Invited talk)

- TH2P1-1 13:50 Manipulation and Characterization of Human Cardiomyocytes for Drug Screening (Invited talk)

Yu Sun; University of Tronto, Canada - TH2P1-2 14:10 Hydrogel Bioelectronics (Invited talk)

Jian-Song Sheng1, Yunfei Zhao1, Yancong Qiao, Jiang Ling, Jun Fu, Yi Yang, Tian-Ling Ren; Tsinghua University, China - TH2P1-3 14:30 Shrink Polymer Micro Sensors for Detection of Water Pollutants (Invited talk)

Tianhong Cui; University of Minnesota, USA - TH2P1-4 14:50 A Flexible Electroencephalography Electronic Skin Based on Graphene

Ge Deng1,2,Yan-cong Qiao1 ,Ning-qin Deng1 ,Xiao-shi Li1 ,Qi Wu1 ,Ying-fen Zeng1,2, Si-fan Yang2, Tian-Ling Ren1; 1Tsinghua University, China 2Graduate School at Shenzhen, Tsinghua University, China - TH2P1-5 15:10 Surface Modification to Improve the Electrochemical Performance of Neural Microelectrode Arrays

Shuguang Yang, Yujie Yang, Liang Geng, George Adedokum, Dongcheng Xie, Ruichen Liu, Lei Xu; University of Science and Technology of China, China

- TH2P1-1 13:50 Manipulation and Characterization of Human Cardiomyocytes for Drug Screening (Invited talk)

- TH2P2-1 13:50 Bionic Eye with Perovskite Nanowire Array Retina (Invited talk)

Leilei Gu, Swapnadeep Poddar, Yuanjing Lin, Zhenghao Long, Daquan Zhang, Qianpeng Zhang, Lei Shu, Xiao Qiu, Matthew Kam, Zhiyong Fan; Hong Kong Univ. of Sci. and Tech, China - TH2P2-2 14:10 β-Ga2O3 Micro-Flake FET SBPD with Record Detectivity of 3.87×1017 Jones for Weak Light Detection

Shunjie Yu1 , Mengfan Ding1 , Wenxiang Mu2 , Zhitai Jia2 , Xiaohu Hou1 , Zhongfang Zhang1 , Pengju Tan1 , Xiaolong Zhao1,Guangwei Xu1 , Shibing Long1; 1University of Science and Technology of China, China; 2Shandong University, China - TH2P2-3 14:30 Large Area and Flexible Organic Active Matrix Image Sensor Array Fabricated by Solution Coating Processes at Low Temperature

Xiao Hou1, Wei Tang1, Sujie Chen1, Jianghu Liang2, Hanyang Xu1, Bang Ouyang1, Ming Li1, Yawen Song1, Chun-chao Chen2, Patrick Too3, Xiaoqing Wei4, Libo Jin4, Gang Qi5, Xiaojun Guo1; 1School of Electronic Information and Electrical Engineering, Shanghai Jiao Tong University, China, 2School of Material Science and Engineering, Shanghai Jiao Tong University, China, 3FlexEnable, UK, 4iRay Technology, China, 5Tianma Microelectronics, China - TH2P2-4 14:50 A Sensitive Vertical Standing Graphene/Silicon Schottky Photodetector to Angle Changes

Ning-Qin Deng1,4 , Zhen-Yi Ju1, Ge Deng1, Hou-Fang Liu1, Xiang-Shun Geng1 , Xiu-Feng Jia1 , Jun Ren1 , Tian-Zhong Yang2 , Dan Xie1 , Yi Yang1 , He Tian1, Tian-Ling Ren1,3; 1Tsinghua University, China, 2Chinese Academy of Sciences, China, 3Center for Flexible Electronics Technology, Tsinghua University, Beijing, China, 4National Institute of Metrology (NIM), Beijing, China - TH2P2-5 15:10 Ultra-High-Sensitivity Photodetector from Ultraviolet to Visible Based on GaDoped In2O3 Nanowire Phototransistor with Top-Gate Structure

Wenhao Ran , Zhen Lou , Guozhen Shen; University of Chinese Academy of Sciences, China

- TH2P2-1 13:50 Bionic Eye with Perovskite Nanowire Array Retina (Invited talk)

- TH2P3-1 13:50 From the Top or Through the Edge: What is the Most Scalable Contact to 2D Semiconductors? (Invited talk)

Aaron D. Franklin; Duke University, USA - TH2P3-2 14:10 Semiconductor Nanostructures for Optoelectronic and Energy Applications (Invited talk)

Hoe Tan; Australian National University, Australia - TH2P3-3 14:30 Small-Hysteresis Flexible Carbon Nanotube Thin-Film Transistors Using Stacked Architecture

Yun Sun1, Dong-Sheng Zhu2,Yang Jian3 ,Chao Zang1, Dong-Ming Sun1; 1Chinese Academy of Sciences, China, 2Shenyang Ligong Univ., China, 3Northeastern Univ. China - TH2P3-4 14:50 Universal Non-Volatile Resistive Switching Behavior in 2D Metal Dichalcogenides Featuring Unique Conductive-Point Random Access Memory Effect

Xiaohan Wu1 , Ruijing Ge1 , Yuqian Gu1 , Emmanuel Okogbue2 , Jianping Shi3 , Abhay Shivayogimath3 , Peter Bøggild4 , Timothy J. Booth4 , Yanfeng Zhang3 , Yeonwoong Jung2 , Jack C. Lee1, Deji Akinwande1 ; 1University of Texas at Austin, Austin, USA, 2University of Central Florida, USA, 3Peking University, China, 4Technical University of Denmark,Denmark - TH2P3-5 15:10 A Study of Materials Impacts on Graphene Electrostatic Discharge Switches

Cheng Li, Mengfu Di, Zijin Pan, Albert Wang; University of California, Riverside, USA

- TH2P3-1 13:50 From the Top or Through the Edge: What is the Most Scalable Contact to 2D Semiconductors? (Invited talk)

- TH2P4-1 13:50 Modeling for assessing Semiconductor Packages in High-Reliability Applications (Invited talk)

Chris Bailey; University of Greenwich, UK - TH2P4-2 14:10 Fan-Out Wafer and Panel Level Packaging - A Platform for 3D Integration (Invited talk)

Tanja Braun1 ,Karl-Friedrich Becker1 ,Michael Töpper1 ,Rolf Aschenbrenner1 ,Martin Schneider-Ramelow2; 1Fraunhofer IZM, Germany, 2Technical University Berlin, Germany - TH2P4-3 14:30 Growth Behavior and Mechanism of Tin Whisker on Isolated SnAg Solder Under Compressive Stress

Shuhui Chen , Xundi Zhang , Lingyue Tan ,Anmin Hu , Huiqin Ling , Ming Li, Tao Hang; Shanghai Jiao Tong University, China - TH2P4-4 14:50 Undercooling and Microstructure Analysis for the Design of Low Melting Point Solder

Li Pu1 , Yongjun Huo1 , Xiuchen Zhao1 , K. N. Tu2 , Yingxia Liu1; 1 Beijing Institute of Technology, China, 2University of California, Los Angeles, USA - TH2P4-5 15:10 An Epoxy Composite Film for Modified Semi-Addictive Process

Suibin Luo, Junyi Yu, Pengpeng Xu, Jie Liu, Shuhui Yu, Rong Sun, Yougen Hu; Chinese Academy of Sciences, China

- TH2P4-1 13:50 Modeling for assessing Semiconductor Packages in High-Reliability Applications (Invited talk)

- TH3P1-1 15:50 Disruptive Technology Elements, and Rapid and Accurate Block-Level Performance Evaluation for 3nm and Beyond (Invited talk)

M.H. Na1, D. Jang1, R. Baert1, S. Sarkar1, S. Patli1, O. Zografos1, B. Chehab1, A. Spessot1, G.Sisto2, P. Schuddinck1, H. Mertens1 , Y.Oniki1 , G. Hellings1 , E. Dentoni Litta1 , J. Ryckaert1 , N.Horiguchi1; 1imec, Belgium, 2Cadence Design System, USA - TH3P1-2 16:10 Advanced CMOS Technologies for Ultra-Low Power Logic and AI Applications (Invited talk)

Shinichi Takagi, Kasidit Toprasertpong, Kimihiko Kato, Kei Sumita , Eishin Nako , Ryosho Nakane, Kwang-won Jo, Mitsuru Takenaka;University of Tokyo, Japan - TH3P1-3 16:30 Subthreshold Swing in Silicon Gate-All-Around Nanowire MOSFET at Cryogenic Temperature

Shohei Sekiguchi, Min-Ju Ahn , Takuya Saraya , Masaharu Kobayashi, Toshiro Hiramoto; University of Tokyo, Japan - TH3P1-4 16:50 Sub-3nm Transition-Metal Dichalcogenides FETs: Theoretical Insights into the Impacts of Layer Numbers and Channel Lengths

Fei Wang, Xiaolei Ma, Wei Wei, Pengpeng Sang, Qianwen Wang, Weiqiang Zhang, Yuan Li, Jiezhi Chen; Shandong University, China - TH3P1-5 17:10 Manipulating the Electrical Characteristics of Two-Dimensional Semiconductor Transistors by Gate Engineering

Jingyi Ma1, Ling Tong1, Xiaojiao Guo1, Xinyu Chen1, Minxing Zhang1, Chenjian Wu2, Wenzhong Bao1; 1Fudan University, China, 2Soochow University, China

- TH3P1-1 15:50 Disruptive Technology Elements, and Rapid and Accurate Block-Level Performance Evaluation for 3nm and Beyond (Invited talk)

- TH3P2-1 15:50 150 mm RF GaN Technology for Commercial RF Applications (Invited talk)

B. Green, K. Moore, S. Klingbeil, C. Rampley, P. Renaud, D. Burdeaux, D. Hill, C. Zhu, J. Wan, K. Kim, C. Gaw, T. Arnold, F. Vanaverbeke, J. Finder; NXP Semiconductors, USA - TH3P2-2 16:10 Nearly Ideal Quasi-Vertical GaN Schottky Barrier Diode with 1010 High On/Off Ratio and Ultralow Turn on Voltage via Post Anode Annealing

Jiabo Chen, Zhihong liu , Zhaoke Bian, haiyong Wang, Xiaoling Duan, Jing Ning, Jincheng Zhang, Yue Hao; Xidian University, China - TH3P2-3 16:30 A Novel Normally-Off Laterally Coupled p-GaN Gate HEMT

Xing Wei1,2, Xiaodong Zhang1,2, Chi Sun1,2, Wenxin Tang1,2, Tao He2 , Xuan Zhang2, Guohao Yu2, Liang Song2 , Wenkui Lin1,2, Yong Cai2, Baoshun Zhang2; 1University of Science and Technology of China, China, 2Suzhou Institute of Nano-Tech and Nano-Bionics, China - TH3P2-4 16:50 Reverse Conduction Induced Dynamic Ron Effect in GaN HEMT with p-GaN Gate

Shaoyu Sun1,2, Ling Xia3, Wengang Wu2, Yufeng Jin1, 2; 1Peking University ShenZhen Graduate School, China, 2Peking University, China, 3Shenzhen Hai Li Technology Inc., China - TH3P2-5 17:10 3D GaN Power Switching Electronics: A Revival of Interest in ELO (Invited talk)

Jia Wang1,2, Hiroshi Amano2, Ya-Hong Xie1 ; 1University of California, Los Angeles, USA, 2Nagoya University, Japan

- TH3P2-1 15:50 150 mm RF GaN Technology for Commercial RF Applications (Invited talk)

- TH3P3-1 15:50 Variability Analysis for Ferroelectric Field-Effect Transistors

Gihun Choe, Shimeng Yu; Georgia Institute of Technology, USA - TH3P3-2 16:10 Revisiting the Definition of Ferroelectric Negative Capacitance Based on Gibbs Free Energy

Yuanyuan Zhang1,2, Xueli Ma1,2, Xiaolei Wang1,2, Jinjuan Xiang1,2, Wenwu Wang1,2; 1Institute of Microelectronics, Chinese Academy of Sciences, China, 2University of Chinese Academy of Sciences, China - TH3P3-3 16:30 Ferroelectric Based FETs and Synaptic Devices for Highly Energy Efficient Computational Technologies (Invited talk)

D. Esseni, R. Fontanini, D. Lizzit, M. Massarotto, F. Driussi, M. Loghi; University of Udine, Italy - TH3P3-4 16:50 On the Critical Role of Ferroelectric Thickness for Negative Capacitance Transistor Optimization

Om Prakash1, Aniket Gupta1,2, Girish Pahwa3, Yogesh S. Chauhan4, Hussam Amrouch5; 1Karlsruhe Institute of Technology, Germany, 2National Institute of Technology Uttarakhand, India, 3University of California, Berkeley, USA, 4 Indian Institute of Technology Kanpur, India, 5 University of Stuttgart, Germany - TH3P3-5 17:10 Modelling and Design of FTJs as High Reading-Impedance Synaptic Devices

R. Fontanini, M. Massarotto, R. Specogna, F. Driussi, M. Loghi, D. Esseni ; University of Udine, Italy

- TH3P3-1 15:50 Variability Analysis for Ferroelectric Field-Effect Transistors

- TH3P4-1 15:50 On-Chip Test Acceleration for Advanced Technologies (Invited talk)

Shenzhi Yang, Fan Lan, Weiwei Pan, Ludan Yang, Yongjun Zheng; Semitronix Inc, China - TH3P4-2 16:10 Efficient Yield Analysis and Optimization with Transient Sensitivity Analysis (Invited talk)

Zuochang Ye, Tsinghua University, China - TH3P4-3 16:30 Statistical Feature Extraction and Hybrid Feature Selection for Material Removal Rate Prediction in Chemical Mechanical Planarization Process

Wenlan Jiang1 , Chunpu Lv1 , Bing Yang2 , Fuquan Zhang2 , Ying Gao2 , Tao Zhang1 , Huangang Wang1; 1Tsinghua University, China, 2Semiconductor Technology Innovation Center (Beijing) Crop, China - TH3P4-4 16:50 Maximizing Output from an Equipment Fleet in a Semiconductor Fab (Invited talk)

Sanjiv Mittal, Haim Albalak, Chris Keith, Willian Nehrer; Applied Materials, USA - TH3P4-5 17:10 Thermal Atomic Layer Etching of Microelectronic Materials (Invited talk)

Steven M. George; University of Colorado, USA

- TH3P4-1 15:50 On-Chip Test Acceleration for Advanced Technologies (Invited talk)

Dual Gate Gas Fet

Day 4 April 11th

Gas Fet

- FR1A1-1 9:00 Physics and Applications of Emerging Ferroelectric Devices (Invited talk)

Masaharu Kobayashi; University of Tokyo, Japan - FR1A1-2 9:20 Dynamics Studies of Polarization Switching in Ferroelectric Hafnium Zirconium Oxide (Invited talk)

X. Lyu1 , M. Si1 , P. R. Shrestha2 , K. P. Cheung2 ,P. D. Ye1; 1Purdue University, USA, 2National Institute of Standards and Technology, Gaithersburg, USA - FR1A1-3 9:40 Top-Gate Short Channel Amorphous Indium-Gallium-Zinc-Oxide Thin Film Transistors with Sub-1.2 nm Equivalent Oxide Thickness

Kaizhen Han, Subhranu Samanta, Chen Sun, Jishen Zhang, Zijie Zheng, Xiao Gong; National University of Singapore, Singapore - FR1A1-4 10:00 Tunable Random Number Generators Implemented by Spin-Orbit Torque Driven Stochastic Switching of a Nanomagnet for Probabilistic Spin Logic

Shuai Zhang, Shihao Li, Xuecheng Zou, Jeongmin Hong, Long You; Huazhong University of Science and Technology, China - FR1A1-5 10:20 100 nm T-Gate GaN-On-Si HEMTs Fabricated with CMOS-Compatible Metallization for Microwave and mm-Wave Applications

Hanlin Xie1,2, Zhihong Liu3, Yu Gao1 , Kenneth E. Lee1 , Geok Ing Ng2; 1Singapore-MIT Alliance for Research and Technology Centre, Singapore, 2Nanyang Technological University, Singapore , 3Xidian University, China

- FR1A1-1 9:00 Physics and Applications of Emerging Ferroelectric Devices (Invited talk)

- FR1A2-1 9:00 Ga2O3 Power Devices and How They Stand up to GaN and SiC (Invited talk)

Huili Grace Xing; Cornell University, USA - FR1A2-2 9:20 Channel Mobility Properties of β-Ga2O3 MOSFETs on Si Substrate Fabricated by Ion-Cutting Process

Yibo Wang,1, Wenhui Xu,2, Genquan Han,1 Tiangui You,2 Haodong Hu,1 Yan Liu,1 Hao Huang,2 Xin Ou,2 Xiaohua Ma,1 Yue Hao1; 1Xidian University, China, 2Chinese Academy of Sciences, China - FR1A2-3 9:40 GaN Super-Heterojunction Schottky Barrier Diode with over 10 kV Blocking Voltage

Sang-Woo Han , Jianan Song ,Rongming Chu; Pennsylvania State University, USA - FR1A2-4 10:00 High Density Packaging Trends Driven by Miniaturization of Home Appliance

Yuquan Su, Jinqing Xu, Chi Zhang, Yasuhiro Koike; GD Midea Air-Conditioning Equipment Co., Ltd., China - FR1A2-5 10:20 Development of High-Frequency Ga2O3 Field-Effect Transistors (Invited talk)

Masataka Higashiwaki; NICT, Japan

- FR1A2-1 9:00 Ga2O3 Power Devices and How They Stand up to GaN and SiC (Invited talk)

- FR1A3-1 9:00 L-UTSOI: Best In-Class Compact Modeling Solution for FD-SOI Technologies (Invited talk)

Thierry Poiroux1 , Sébastien Martinie1 , Olivier Rozeau1 , Michael Reiha2 , Julien Arcamone1; 1MINATEC Campus, France, 2Univ. Grenoble Alpes, France - FR1A3-2 9:20 RF Linearity of SiGe HBT: Physics, Compact Modeling Using Mextram 505 and X-Parameter Based Measurements (Invited talk)

Guofu Niu1, Yiao Li1, Xuewei Ding1, Anni Zhang1, Huaiyuan Zhang1 Andries Scholten2, Marnix Willemsen2, Ralf Pijper2, Luuk F. Tiemeijer2; 1Auburn University, USA, 2NXP Semiconductors, The Netherlands - FR1A3-3 9:40 Evaluating the Impact of STI Recess Profile Control on Advanced FinFET Device Performance

Qingpeng Wang, Yu De Chen, Rui Bao, Cheng Li, Jacky Huang, Joseph Ervin; Lam Research company, China - FR1A3-4 10:00 Multi-Physics Evaluation of Silicon Steep-Slope Cold Source FET

Weizhuo Gan1,5, Raphaël Prentki3 , Kun Luo1 , Jiali Huo1,5, Weixing Huang1,5, Qiang Huo1,5,Jianhui Bu5 , Ronggen Cao6 , Ye Lu2 , Huaxiang Yin1,5, Hong Guo3 , Zhenhua Wu1,5; 1Institute of Microelectronics, Chinese Academy of Sciences, China, 2School of Information Science and Technology, Fudan University, Shanghai, China, 3McGill University, Canada, 5University of Chinese Academy of Sciences, China, 6Department of materials, Fudan University, China - FR1A3-5 10:20 Enhanced On-State Current in Barrier-Free Carbon Heterojunction Tunneling Field-Effect Transistor

Yu Zhu1, Wenli Zhou1,2, Li Cheng1, Qingfeng Gong1; 1Huazhong University of Science and Technology, China 2Wuhan National Laboratory of Optoelectronics, China

- FR1A3-1 9:00 L-UTSOI: Best In-Class Compact Modeling Solution for FD-SOI Technologies (Invited talk)

- FR1A4-1 9:00 Current status of SiC bulk single crystal growth processes (Invited talk)

Bing Gao; Wuhan University, China - FR1A4-2 9:20 Tailoring the electromechanical coupling in stretchable inorganic thin-film electronics (Invited talk)

Yuan Lin; University of Electronic Science and Technology of China, China - FR1A4-3 9:40 Synaptic Plasticity in Novel Non-Volatile FET with Amorphous Gate Insulator Enabled by Oxygen Vacancy Related Dipoles

Guoqing Zhang1 , Yue Peng1, Wenwu Xiao1, 2, Fenning Liu1 , Yan Liu1 , Genquan Han1, Yue Hao1; 1Xidian University, China, 2Xi’an UniIC Semiconductors, China - FR1A4-4 10:00 Selecting and Optimizing Threshold Switching Materials and Devices for Stochastic Neuron

Kuan Wang, Qing Hu, Qi Lin, Dayou Zhang, Yuhui He, Hao Tong, Xiangshui Miao; Huazhong University of Science and Technology, China - FR1A4-5 10:20 High-Performance ZnO Thin-Film Transistors Prepared by Atomic Layer Deposition at Low Temperature

Qi Li, Junchen Dong, Dedong Han, Xing Zhang, Yi Wang; Peking University, China

- FR1A4-1 9:00 Current status of SiC bulk single crystal growth processes (Invited talk)

- FR2A1-1 11:00 Low Frequency Noise: A Show Stopper for State-Of-The-Art and Future Si, Ge-Based and III-V Technologies (Invited talk)

C. Claeys1 , A. Oliviera2 , A. Veloso3 , L. He4 , K. Takakura5 , V. Putcha3 , H. Amimura3 , E. Simoen3; 1KU Leuven, Belgium 2Universidade Tecnológica Federal do Paraná (UTFPR) , Brazil, 3Imec, Belgium, 4Xidian University, China, 5National Institute of Technology (KOKEN), Kumamoto College, Japan - FR2A1-2 11:20 A Review of Recent MOSFET Source and Drain Resistances Extraction Methods Using a Single Test Device (Invited talk)

Adelmo Ortiz-Conde1, Manuel A. Quevedo-Lopez2; 1Universidad Simón Bolívar,Venezuela,2University of Texas at Dallas, USA - FR2A1-3 11:40 White Noise Characterization of N-MOSFETs for Physics-Based Cryogenic Device Modeling

K. Ohmori, S. Amakawa; Device Lab Inc., Japan - FR2A1-4 12:00 MOSFET C-V Characteristics Extraction Based on Ring Oscillator with Addressable DUTs

Zhen Zhou1 , Junxu Wu2 , Changfeng Wang2 , Ganbing Shang2 , Xiaojin Li1 , Yabin Sun1 , Yanling Shi1; 1East China Normal University, China, 2Shanghai Huali Microelectronics Corporation, China - FR2A1-5 12:20 Performance Trade-Offs in Complementary FET (CFET) Device Architectures for 3nm-Node and Beyond

Xiaoqiao Yang1 , Yabin Sun1, Ziyu Liu2, Yanling Shi1, Xiaojin Li1; 1East China Normal University, China, 2Fudan University, China

- FR2A1-1 11:00 Low Frequency Noise: A Show Stopper for State-Of-The-Art and Future Si, Ge-Based and III-V Technologies (Invited talk)

- FR2A2-1 11:00 Phonon Properties of Group IV Materials for Thermoelectric Applications (Invited talk)

Atsushi Ogura1, 2, Ryo Yokogawa1, 2; 1School of Science and Technology, Meiji University, Japan 2Meiji Renewable Energy Laboratory, Meiji University, Japan - FR2A2-2 11:20 Progress and Future Challenges of SiC Power MOSFETs (Invited talk)

Tsunenobu Kimoto; Kyoto University, Japan - FR2A2-3 11:40 Novel Ultralow On-Resistance Accumulation-Mode LDMOS with Integrated Diodes

Jie Wei, Zhen Ma, Congcong Li, Kaiwei Dai, Xiaorong Luo, Bo Zhang; University of Electronic Science and Technology of China, China - FR2A2-4 12:00 Process Improvement for Stabilizing the VLD Effective Dose of 4500V Trench-Gated IGBT Platform

Rui Jin1, Li Li1, Kui Pu2, Jun Zeng2,3, Longlai Xu2 , Xiaohu Deng4, Pan Yin4, Yaohua Wang1, Wenhong Zhang2, Mohamed N. Darwish2,3; 1Global Energy Interconnection Research Institute co., Ltd.,China, 2MaxPower Semiconductor Inc., China, 3 MaxPower Semiconductor Inc., USA,4China Resource Microelectronics Limited, China - FR2A2-5 12:20 Accurate TCAD Simulation of Trench-Gate IGBTs and Its Application to Prediction of Carrier Lifetime Requirements for Future Scaled Devices (Invited talk)

M. Watanabe1 , N. Shigyo1 , T. Hoshii1 , K. Furukawa1 , K. Kakushima1 , K. Satoh2 , T. Matsudai3 , T. Saraya4 , T. Takakura4 , I. Muneta1 , H. Wakabayashi1 , A. Nakajima5 , S. Nishizawa6 , K. Tsutsui1 , T. Hiramoto4 , H. Ohashi1 , H. Iwai1; 1Tokyo Institute of Technology, Japan, 2Mitsubishi Electric Corp., Japan, 3Toshiba Electronic Devices & Storage Corp., Japan, 4University of Tokyo, Japan, 5Nat. Inst. Advanced Industrial Science and Technology, Japan,6Kyushu University, Japan

- FR2A2-1 11:00 Phonon Properties of Group IV Materials for Thermoelectric Applications (Invited talk)

- FR2A3-1 11:00 A Compact Model of Analog RRAM Considering Temperature Coefficient for Neural Network Evaluation

Minghong Xu1, Bin Gao1, Feng Xu1, Wei Wu1, Jianshi Tang1, Jiezhi Chen2, He Qian1; 1Tsinghua University, China, 2Shandong University, China - FR2A3-2 11:20 Development of Integrated Device Simulator for Quantum Bit Design: Self-Consistent Calculation for Quantum Transport and Qubit Operation

Hidehiro Asai, Shota Iizuka, Tsutomu Ikegami, Junichi Hattori, Koichi Fukuda, Hiroshi Oka, Kimihiko Kato, Hiroyuki Ota, Takahiro Mori; National Institute of Advanced Industrial Science and Technology (AIST), Japan - FR2A3-3 11:40 Designing EDA-Compatible Cryogenic CMOS Platform for Quantum Computing Applications

Zewei Wang1 , Chengwei Cao2 , Puqing Yang1,3, Yumeng Yuan1 , Zhidong Tang1 , Renhe Chen1 , Weican Wu2 , Xin Luo2 , Ao Guo2 , Liujiang Yu4 , Ganbing Shang4 , Zhaofeng Zhang3 , Shaojian Hu2 , Xufeng Kou1; 1ShanghaiTech University, China, 2Shanghai IC Research and Development Center, China, 3Chinese Academy of Sciences, China, 4Huali Microelectronics Corporation (HLMC), China - FR2A3-4 12:00 Compact Modeling of Organic and IGZO TFTs from 150K to 350K (Invited talk)

Benjamin Iñiguez1 , Harold Cortés-Ordóñez1 , Gérard Ghibaudo2 , Antonio Cerdeira3 , Magali Estrada3 ; 1University Rovira i Virgili, Spain, 2MINATEC/INPG ,France, 3CINVESTAV, Mexico - FR2A3-5 12:20 Compact Physics-Based Charge Core Model for CAAC In-Ga-Zn Oxide Multi-Gate FETs

Slobodan Mijalkovic1, Bogdan Tudor1, Makoto Watanabe1, Hitoshi Kunitake2, Takayuki Ikeda2, Shunpei Yamazaki2; 1Silvaco, Inc., USA, 2Semiconductor Energy Laboratory Co., Japan

- FR2A3-1 11:00 A Compact Model of Analog RRAM Considering Temperature Coefficient for Neural Network Evaluation

- FR2A4-1 11:00 RF Silicon Technologies and Its Reliability for Sub-6GHz and mmWave 5G Applications (Invited talk)

P. Srinivasan; GLOBALFOUNDRIES Inc., USA - FR2A4-2 11:20 Re-Consideration of Influence of Fluorine on SiO2 and SixNy Reliabilities (Invited talk)

Yuichiro Mitani; Tokyo City University, Japan - FR2A4-3 11:40 ESD Co-Design of mm-Wave RF Switch in 22nm SOI

Feilong Zhang, Cheng Li, Mengfu Di, Zijin Pan, Han Wang, Albert Wang; University of California, Riverside, USA - FR2A4-4 12:00 Experimental Understanding of the Impact of Channel Percolation on Low Frequency Noise Using Transient Enhanced Diffusion of Channel Dopants

Shuntaro Fujii, Soichi Morita, Tsutomu Miyazaki; Asahi Kasei Microsystems, Japan - FR2A4-5 12:20 Design for Reliability based on Customer Obsession (Invited talk)

Owen Liu; Amazon Corp., Product Integrity, China

- FR2A4-1 11:00 RF Silicon Technologies and Its Reliability for Sub-6GHz and mmWave 5G Applications (Invited talk)

- FR3P1-1 14:00 Nanosheet FETs and Their Potential for Enabling Continued Moore's Law Scaling (Invited talk)

A. Veloso, G. Eneman, A. De Keersgieter, D. Jang, H. Mertens, P. Matagne, E. Dentoni Litta, J. Ryckaert, N. Horiguchi; Imec, Belgium - FR3P1-2 14:20 Technology Trends in 2.5D/3D Packaging and Heterogeneous Integration (Invited talk)

Masaya Kawano ; Institute of Microelectronics, A*STAR, Singapore - FR3P1-3 14:40 Optimization of Contact W Related Processes for 28/22 nm HKMG Technology Node

Hai-Jin Lu, Zong-Yan Pan, Pei-Yu Chen, Zhi-Cheng Zhang, Ming-Zhi Chen; Shanghai Huali Microelectronics Corporation, China - FR3P1-4 15:00 Formation Mechanism of a Rounded SiGe-Etch-Front in an Isotropic Dry SiGe Etch Process for Gate-All-Around (GAA)-FETs

Yu Zhao, Taku Iwase, Makoto Satake, Hirotaka Hamamura; Hitachi, Ltd., Japan - FR3P1-5 15:20 Optimization of Bump Defect at High-Concentration In-Situ Phosphorus Doped Polysilicon/TEOS Oxide Interface for 3D NAND Flash Memory Application

Dongxue Zhao1,2,3, Zhiliang Xia1,2,3, Linchun Wu3 , Tao Yang1,2,3, Dongyu Fan1,2,3, Yuancheng Yang3 , Lei Liu3 , Wenxi Zhou3 , Zongliang Huo1,2,3; 1Institute of Microelectronics of the Chinese Academy of Sciences, China, 2University of Chinese Academy of Sciences, China, 3Yangtze Memory Technologies Company, Ltd., China

- FR3P1-1 14:00 Nanosheet FETs and Their Potential for Enabling Continued Moore's Law Scaling (Invited talk)

- FR3P2-1 14:00 Flexible and Wearable Sensing Electronics (Invited talk)

Ting Zhang; Suzhou Institute of Nano‐Tech and Nano‐Bionics, China - FR3P2-2 14:20 Emerging Designs for Polymer-Based Optoelectronics and Energy Storage (Invited talk)

Tse Nga Ng; University of Califonria San Diego, USA - FR3P2-3 14:40 Highly Stable Fibrous Solid-State Ag/AgCl Reference Electrode

Chaochao Shen, Xin Xi, Wei Tang, Xiaojun Guo, Ruili Liu; Shanghai Jiao Tong University, China - FR3P2-4 15:00 Fabrication of Highly Sensitive Flexible Tactile Sensor with Hierarchical Microstructures for Wearable Electronics

Qifeng Du1, Ying Chen1,2, Zhijian Wang1 , Jun Ai1 , Baicheng Zhang1 , Lanlan Liu1 , Xue Feng3; 1Institute of Flexible Electronics Technology of THU, China. 2Qiantang Science and Technology Innovation Center, China,3Tsinghua University, China - FR3P2-5 15:20 Printed Stretchable Multifunctional E-Textile for Wearable Electronics

Bin Tian, Wei Wu; Wuhan University, China

- FR3P2-1 14:00 Flexible and Wearable Sensing Electronics (Invited talk)

- FR3P3-1 14:00 Implementation, Operation and Applications of Memristive Neural Networks (Invited talk)

Qiangfei Xia; University of Massachusetts, USA - FR3P3-2 14:20 In-memory computing with memristor content addressable memory circuits (Invited talk)

Catherine Graves; HP Labs, USA - FR3P3-3 14:40 A Neural Network-Based Harmonic Suppression Algorithm for Medium-To-High Resolution ADCs (Invited talk)

Xizhu Peng1, Yihang Mi1 , Yunfan Zhang1 , Yao Xiao1 , Wei Zhang1 , Yong Tang1 , He Tang1,2; 1 University of Electronic Science and Technology of China, China, 2Guangdong Institute of electronic information engineering, University of Electronic Science and Technology of China, China - FR3P3-4 15:00 Artificial Neuron with Spike Frequency Adaptation Based on Mott Memristor

Qiumeng Wei1, Jianshi Tang1,2, Xinyi Li1, Yanan Zhong1, Bin Gao1,2, He Qian1,2, Huaqiang Wu1,2; 1Institute of Microelectronics, Tsinghua University, China, 2Beijing Innovation Center for Future Chips (ICFC), Tsinghua University, China - FR3P3-5 15:20 Associative Learning Circuit Based on Synaptic Transistors with Temporal Dynamics

Chang Liu, Zhaokun Jing, Yuchao Yang, Ru Huang; Peking University, China

- FR3P3-1 14:00 Implementation, Operation and Applications of Memristive Neural Networks (Invited talk)

- FR3P4-1 14:00 Applications of AI Technologies in Flash Memory Business (Invited talk)

Ryohei Orihara; Digital Process Innovation Center Kioxia Corporation, Japan - FR3P4-2 14:20 Applications for Machine Learning in Semiconductor Manufacturing and Test (Invited talk)

Chen He1 , Hanbin Hu2 , Peng Li2; 1NXP Semiconductors, Austin, USA, 2University of California at Santa Barbara, USA - FR3P4-3 14:40 Machine Learning Approaches Optimizing Semiconductor Manufacturing Processes (Invited talk)

Tsuyoshi Moriya; Tokyo Electron Limited, Japan - FR3P4-4 15:00 Applications for Machine Learning in Semiconductor Manufacturing (Invited talk)

Richard Burch, Luke Merrick, Qing Zhu, Tomonori Honda, Jeff David; PDF Solutions, USA - FR3P4-5 15:20 Improving accuracy and cycle-time in computational lithography with Machine Learning (Invited talk)

Shibing Wang; ASML, Netherlands